BCDMOS 특징

- Bipolar (BJT): 높은 전류 구동 능력과 증폭 특성을 제공하여 고전류 응용에 적합합니다.

- CMOS (Complementary Metal-Oxide-Semiconductor): 저전력 소모와 고밀도 집적이 가능하여 디지털 회로와 제어 회로에 유리합니다.

- DMOS (Double-diffused MOSFET): 고전압 구동과 저항 특성이 우수하여 전력 제어 응용에 적합합니다.

BCDMOS의 장점

- 고전압 구동 가능: DMOS의 특성을 활용하여 수백 볼트까지 제어 가능.

- 고속 동작: CMOS의 속도와 Bipolar의 고속 증폭 능력을 결합.

- 집적화 가능: 하나의 칩에서 고전력과 고속 신호 처리가 모두 가능.

- 효율적 전력 관리: 전력 소모를 최소화하며 다양한 기능을 구현.

응용 분야

- 전력 관리 IC(PMIC)

- 모터 제어 드라이버

- DC-DC 컨버터

- 자동차 전자장치(전장 부품)

- 통신 및 전원 제어 모듈

BCDMOS의 전형적인 애플리케이션

BCDMOS 기술을 사용하는 대표적인 애플리케이션은 다음과 같습니다:

- 전력 관리 IC (PMIC)

- BJT로 전류 증폭, DMOS로 고전압 제어, CMOS로 디지털 제어를 수행

- DC-DC 컨버터

- BJT로 출력 전류 증폭, DMOS로 전압 스위칭, CMOS로 제어 회로 구성

- 모터 드라이버 IC

- BJT로 고전류 구동, DMOS로 전압 제어, CMOS로 속도 및 방향 제어

- 통신 및 RF 증폭기

- BJT로 신호 증폭, DMOS로 전력 제어, CMOS로 제어 신호 처리

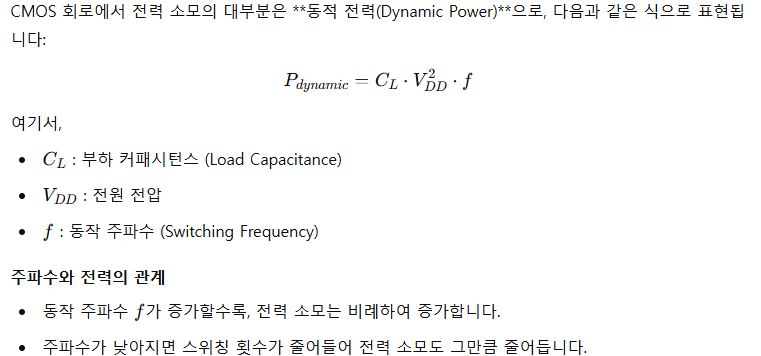

> CMOS (Complementary Metal-Oxide-Semiconductor)가 저전력 소모와 고밀도 집적이 가능하여 디지털 회로와 제어 회로에 유리한 이유

1. 저전력 소모 (Low Power Consumption)

CMOS 회로는 PMOS와 NMOS 트랜지스터를 한 쌍으로 사용하여 전류가 흐를 때와 흐르지 않을 때의 상태를 제어합니다.

- 스태틱 전력 소모가 거의 없음: CMOS는 논리적으로 “0” 또는 “1” 상태에 있을 때 전류가 거의 흐르지 않기 때문에 스태틱 전력이 거의 소모되지 않습니다.

- 전력 소모는 스위칭 시에만 발생: 트랜지스터가 스위칭(상태 전환)할 때에만 짧은 시간 동안 전류가 흐르므로 동적 전력 소모만 고려하면 됩니다.

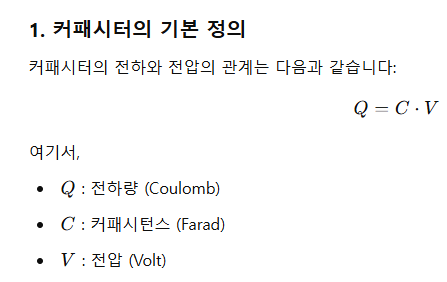

- 캐패시턴스 충전/방전 전력: 스위칭 시에만 캐패시턴스를 충전하거나 방전하면서 전력이 소모되기 때문에, 동작 주파수가 낮을수록 전력 소모가 감소합니다.

- 2. 캐패시턴스 충전/방전 전력 소모

- 주파수가 높으면 스위칭 횟수가 많아져 캐패시턴스를 충전/방전하는 작업이 자주 일어납니다.

- 주파수가 낮으면 스위칭 횟수가 줄어들어 충전/방전 횟수도 감소하여 전력 소모가 줄어듭니다.

3. 스위칭 손실 감소- 이로 인해 순간적으로 전류가 흐르며 전력이 소모되는데, 주파수가 낮으면 이러한 스위칭 손실도 줄어듭니다.

4. 발열 감소와 안정성 향상- 주파수를 낮추면 자연스럽게 발열도 줄어들어 안정적 동작이 가능해집니다.

- 소모된 전력이 대부분 열로 전환

- 또한 온도가 높아지면 전자 이동도 감소, 누설 전류 증가 등으로 인해 성능이 떨어지고 회로 안정성이 저하됨

- 발열이 증가하면 Leakage Current도 증가 (온도가 높아질수록 자유 전자와 정공 쌍 생성이 증가함 > 캐리어가 증가하고 밴드갭이 줄어들 수 있음)

- 또한 subthreshold Leakage Current 가 증가

- CMOS 회로에서 동작 주파수가 낮을 때 전력 소모가 줄어드는 이유는 스위칭 횟수 감소로 인한 동적 전력 소모 감소와 스위칭 손실 감소 때문입니다.

따라서 저전력 애플리케이션에서는 동작 주파수를 낮추거나 전원 전압을 줄이는 기술이 활용됩니다. - 동작 주파수가 높을수록 소모되는 전력이 발열로 이어지며, 이를 제어하기 위해 추가적인 방열 설계가 필요합니다.

- 스위칭이 빈번할수록 트랜지스터가 ON/OFF 상태를 빠르게 전환하면서 짧은 순간이지만 **둘 다 켜져 있는 상태(쇼트 서킷 상태)**가 발생할 수 있습니다.

- CMOS 회로는 전압 변환 시 캐패시턴스를 충전하거나 방전하는 과정에서 전력을 소모합니다.

2. 캐패시턴스 충전/방전 전력 소모

CMOS 회로는 전압 변환 시 캐패시턴스를 충전하거나 방전하는 과정에서 전력을 소모합니다.

- 주파수가 높으면 스위칭 횟수가 많아져 캐패시턴스를 충전/방전하는 작업이 자주 일어납니다.

- 주파수가 낮으면 스위칭 횟수가 줄어들어 충전/방전 횟수도 감소하여 전력 소모가 줄어듭니다

2. 고밀도 집적 (High Density Integration)

CMOS는 고밀도 집적을 구현할 수 있는 특성 덕분에 디지털 회로에 특히 적합합니다.

- 소형 트랜지스터 구조: PMOS와 NMOS 트랜지스터를 동일 기판에 집적할 수 있어 면적이 적게 소모됩니다.

- 공정 기술의 발전: 미세공정 기술이 발전하면서 더 작은 크기의 CMOS 소자를 구현할 수 있어 집적도가 매우 높아졌습니다.

- 레이아웃의 유연성: CMOS 구조는 다양한 디지털 로직 게이트를 효과적으로 집적할 수 있는 유연성을 제공합니다.

3. 디지털 및 제어 회로에 유리한 이유

- 신호 무결성 보장: CMOS는 높은 노이즈 마진을 제공하여 디지털 신호의 왜곡을 최소화할 수 있습니다.

- 논리 게이트의 구현 용이: CMOS를 사용하면 기본 논리 게이트(NAND, NOR 등)를 효율적으로 구현할 수 있어 디지털 회로 설계에 적합합니다.

- 전력 효율성: 저전력 특성이 특히 배터리 기반 휴대기기 및 저전력 애플리케이션에 유리합니다.

🌀 4. 전압 전송 특성 (VTC)의 안정성

CMOS 인버터의 전압 전송 특성(VTC) 곡선을 보면,

- 출력 전압이 입력 전압 변화에 민감하지 않은 영역이 존재합니다.

- 이 구간에서 출력 전압은 거의 변화하지 않기 때문에 노이즈 내성이 강합니다.

CMOS 인버터의 전압 전송 특성 곡선

- 출력 전압이 High 또는 Low 상태일 때 기울기가 거의 0에 가깝습니다.

- 따라서 소량의 노이즈 전압이 입력되어도 출력 신호는 변화하지 않고 안정적입니다.

⚡ 5. 높은 임피던스 특성

CMOS 회로는 출력 임피던스가 높기 때문에 외부로부터의 전류 유입이 적습니다.

- 노이즈 전압이 걸리더라도 전류 흐름이 적어 신호 왜곡 가능성이 낮습니다.

- 또한, CMOS는 입력 시 고저항 특성을 가져 외부로부터 유입되는 노이즈를 효과적으로 차단합니다.

💡 1. 임피던스가 높다는 것의 의미

**임피던스(Impedance)**는 전기 회로에서 전류의 흐름을 방해하는 정도를 나타냅니다.

- 단위: 옴(Ω)

- 임피던스가 높으면 전류가 잘 흐르지 않음을 의미합니다.

- 반대로, 임피던스가 낮으면 전류가 쉽게 흐릅니다.

🌊 물에 비유하면?

- 높은 임피던스는 좁은 수도관 같아서 물이 거의 안 지나가는 것과 같아요.

- 낮은 임피던스는 넓은 수도관 같아서 물이 쉽게 지나갑니다.

🔌 2. CMOS의 높은 임피던스 특성

CMOS 회로에서 특히 입력 임피던스가 매우 높습니다.

- CMOS 회로의 입력 단자는 거의 전류가 흐르지 않는 특성을 가지고 있습니다.

- 왜냐하면 CMOS의 입력은 **게이트 전압으로 제어되는 전계 효과 트랜지스터(FET)**이기 때문입니다.

- 게이트 전극은 산화막으로 절연되어 있어 전류가 거의 흐르지 않습니다.

⚡ CMOS 인버터의 입력 특성

- PMOS와 NMOS의 게이트 단자는 전기적으로 절연되어 있어 전류가 흐르지 않습니다.

- 즉, 입력 전류가 거의 0에 가까워 외부 신호가 걸리더라도 큰 영향을 받지 않습니다.

🌀 3. 왜 신호 왜곡이 줄어드는가?

(1) 노이즈 전류 유입 차단

- 높은 임피던스를 가지면 외부로부터의 전류 유입이 적습니다.

- 외부 잡음이나 노이즈가 입력 단자에 걸리더라도 전류가 거의 흐르지 않으므로 출력에 영향을 주지 않습니다.

(2) 신호 왜곡 최소화

- 전류가 거의 흐르지 않기 때문에, 입력 신호가 왜곡될 가능성이 매우 낮습니다.

- 따라서 디지털 신호의 High와 Low 상태가 명확히 구분됩니다.

🚧 4. 높은 임피던스가 주는 장점

- 노이즈 내성 향상: 외부에서 들어오는 잡음 전류가 흐르지 않아서 신호 왜곡이 줄어듭니다.

- 전력 소모 감소: 입력 전류가 거의 없으므로 전력 소모가 극히 적습니다.

- 신호 간섭 감소: 인접 회로나 주변 소자의 영향을 덜 받습니다.

💭 쉽게 예를 들어볼게요!

📱 스마트폰 터치스크린

스마트폰 화면을 터치할 때 손가락으로 접촉하면 미세한 전류가 흐르는데,

- 만약 임피던스가 낮다면 작은 잡음이나 전자기파에도 화면이 오작동할 수 있습니다.

- 하지만 CMOS 회로의 높은 임피던스 덕분에, 터치 신호 외의 잡음에 민감하지 않게 설계할 수 있습니다.

📝 정리

- 높은 임피던스는 전류 흐름을 방해해서 외부 전류 유입이 거의 없습니다.

- 잡음 전류가 들어와도 흐르지 않으므로 신호 왜곡이 적습니다.

- CMOS 회로의 입력 단자가 고저항 상태이기 때문에 외부 간섭에 강하고 전력 소모도 적습니다.

결론적으로, CMOS 회로는 높은 입력 임피던스 덕분에 신호 무결성이 뛰어나며, 노이즈나 잡음에 영향을 받지 않고 안정적으로 동작할 수 있습니다!

🛠️ 6. 전력 소모 특성

CMOS는 스위칭 시에만 전력을 소모하기 때문에 정적 상태에서 노이즈가 발생하더라도 내부 전압이 거의 변하지 않습니다.

- 이는 신호 왜곡을 줄이는 데 큰 도움이 됩니다.

- 전력 소모가 적을수록 온도 상승도 줄어들어 온도에 의한 노이즈 유발 가능성도 줄어듭니다.

💡 7. 종합 정리

- 명확한 전압 구분: "0"과 "1"의 전압 차이가 커서 상태 변화가 어려움

- 급격한 상태 전환 특성: 임계 전압을 기준으로 급격히 변환하여 노이즈가 쉽게 영향을 주지 못함

- 높은 임피던스 특성: 외부 신호 간섭에 강함

- 전력 소모 감소 효과: 정적 상태에서 전력 소모가 적어 발열로 인한 노이즈 증가가 적음

결론

CMOS 기술이 디지털 회로와 제어 회로에 유리한 이유는 저전력 소모와 고밀도 집적이 가능하기 때문입니다. 이러한 특성 덕분에 스마트폰, 마이크로컨트롤러, 프로세서 등 대부분의 디지털 전자 기기에 광범위하게 활용되고 있습니다.

'반도체 > FOUNDRY' 카테고리의 다른 글

| 반도체/FOUNDRYBCDMOS - DMOS (0) | 2025.03.27 |

|---|---|

| BCDMOS - BJT (0) | 2025.03.25 |